Intel hat heute Morgen einige der feineren architektonischen und technischen Details seines kommenden Lunar Lake SoC enthüllt – dem Chip, der die nächste Generation der mobilen Core Ultra-Prozessoren sein wird. Wieder einmal veranstaltete Intel eine seiner zunehmend regelmäßigen Tech-Tour-Veranstaltungen für Medien und Analysten, und dieses Mal richtete Intel kurz vor Beginn der Computex 2024 seinen Sitz in Taipeh ein. Während der Tech Tour enthüllte Intel mehrere Aspekte von Lunar Lake, darunter das neue P. Das Grunddesign trägt einen Codenamen Löwenbucht Und eine neue Welle von Elektronenkernen, die ein wenig wie die bahnbrechenden Niedrigenergie-Elektronenkerne von Meteor Lake aussehen. Außerdem wurde die Intel NPU 4 vorgestellt, die laut Intel bis zu 48 TOPS liefert und damit die Microsoft Copilot+-Anforderungen für die neue Ära der KI-fähigen PCs übertrifft.

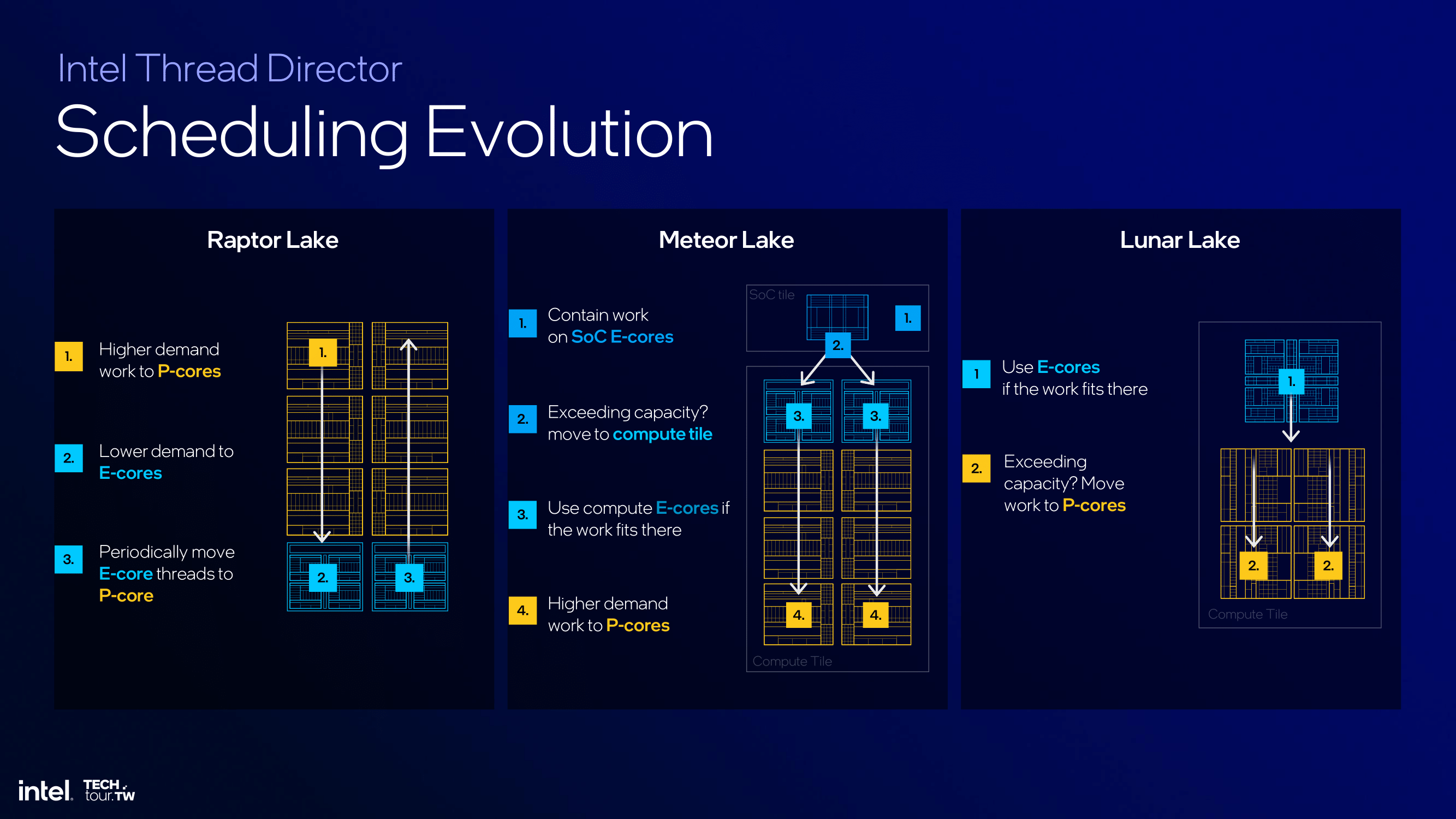

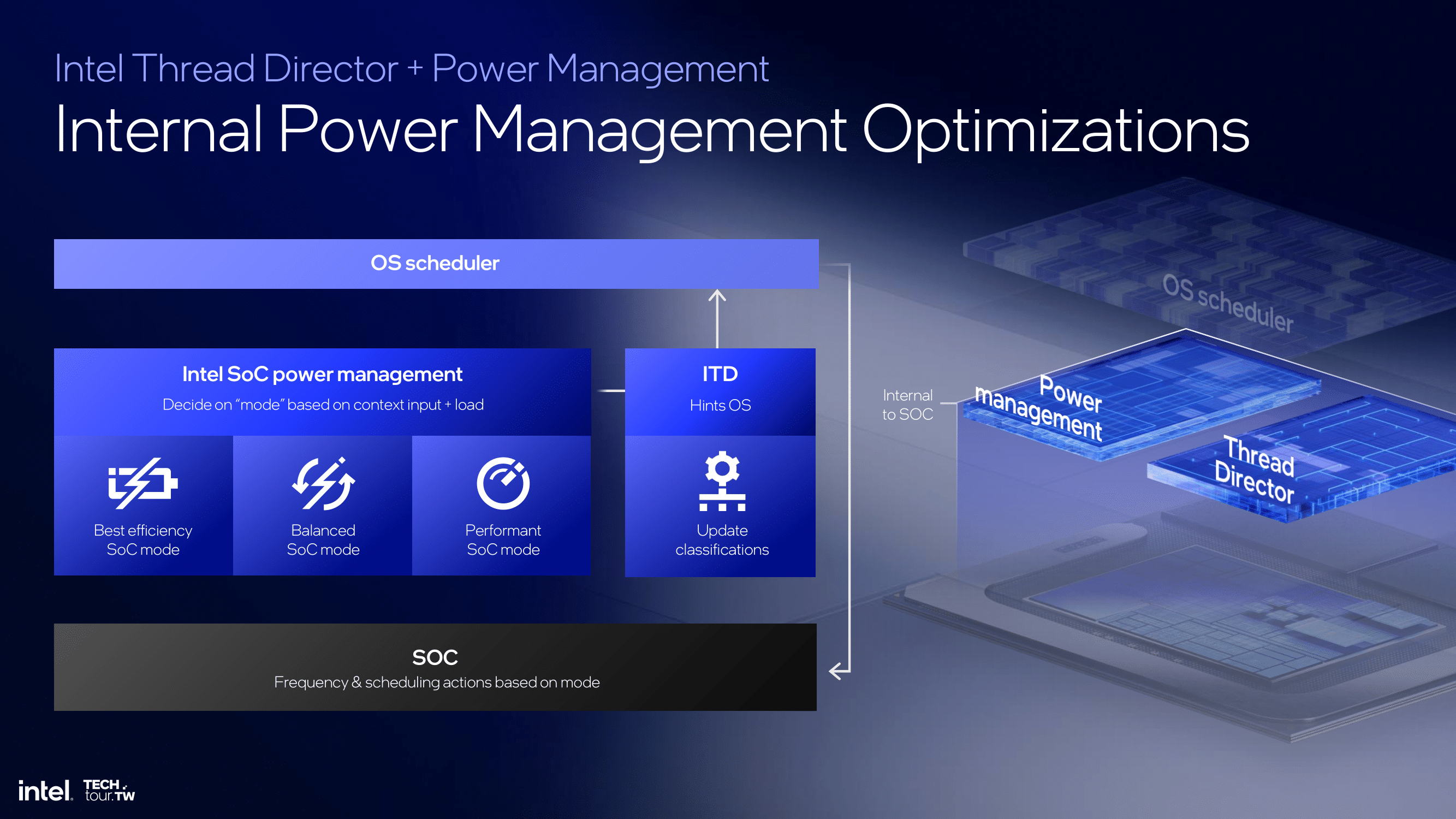

Intels Lunar Lake stellt eine strategische Weiterentwicklung seines mobilen SoC-Portfolios dar und baut auf der Einführung von Meteor Lake im letzten Jahr auf, wobei der Schwerpunkt auf der Verbesserung der Energieeffizienz und der allgemeinen Leistung liegt. Lunar Lake weist Aufgaben basierend auf den Arbeitslastanforderungen dynamisch effizienten Kernen (E-Kernen) oder Leistungskernen (P-Kernen) zu, indem es fortschrittliche Planungsmechanismen nutzt, die eine optimale Energienutzung und Leistung gewährleisten sollen. Aber auch hier spielt Intel Thread Director zusammen mit Windows 11 eine entscheidende Rolle, indem er den Betriebssystemplaner anweist, in Echtzeit Anpassungen vorzunehmen, die Effizienz und Rechenleistung je nach Schwere der Arbeitslast in Einklang bringen.

| Generationen der Intel-CPU-Architektur | |||||

| Erle/Raptor Lake | Meteor See |

Mond- See |

Pfeil See |

Tiger See |

|

| P-Core-Architektur | goldene Bucht/ Raptor Cove |

Redwood Cove | Löwenbucht | Löwenbucht | Cougar Cove? |

| Grundlegende elektronische Architektur | Gracemont | Crestmont | Skymont | Crestmont? | Darkmont? |

| Architektur der Grafikprozessoreinheit | XE-LP | XE-LPG | Xe2 | XE2? | ? |

| Architektur NPU | Nichts | NBU 3720 | Nationale Einheit 4 | ? | ? |

| Aktive Kacheln | 1 (homogen) | 4 | 2 | 4? | ? |

| Herstellungsprozess | Intel 7 | Intel 4 + TSMC N6 + TSMC N5 | TSMC N3E + TSMC N6 | Intel 20A + mehr | Intel 18A |

| Scheibe | Mobil + Desktop | Ziehen um | LB Mobile | HP Mobile + Desktop | Ziehen um? |

| Erscheinungsdatum (OEM) | Viertes Quartal 2021 | Viertes Quartal 2023 | Drittes Quartal 2024 | Viertes Quartal 2024 | 2025 |

Lunar Lake: Entworfen von Intel, gebaut von TSMC

Obwohl es viele Aspekte von Lunar Lake gibt, in die Sie eintauchen können, ist es vielleicht am besten, mit dem zu beginnen, was sicherlich am bemerkenswertesten ist: wer es gebaut hat.

Intels Lunar-Lake-Kacheln werden nicht in einer eigenen Gießerei hergestellt – eine deutliche Abkehr vom historischen Vorbild und sogar vom modernen Meteor Lake, wo Rechenkacheln mithilfe des Intel-4-Prozesses hergestellt werden. Stattdessen werden beide Lunar-Lake-Kacheln getrennt bei TSMC hergestellt , unter Verwendung einer Kombination aus TSMC N3E- und N6-Prozessen. Im Jahr 2021 hat sich Intel zum Ziel gesetzt, seine Chip-Design-Stacks zu entlasten, um die bestmögliche Foundry – ob intern oder extern – zu nutzen, und nirgendwo ist dies deutlicher als hier.

Insgesamt stellt Lunar Lake die zweite Generation der maßgeschneiderten SoC-Architektur für den Mobilfunkmarkt dar und ersetzt die Meteor-Lake-Architektur im Low-End-Bereich. Zu diesem Zeitpunkt gab Intel bekannt, dass es ein 4P+4E-Design (8 Kerne) mit deaktiviertem Multi-Threading/SMT verwendet, sodass die Gesamtzahl der vom Prozessor unterstützten Threads einfach der Anzahl der CPU-Kerne entspricht, z. B. 4P+ 4E /8 T.

Der Lunar-Lake-Build kombiniert eine synergetische Zusammenarbeit zwischen dem Architekturdesignteam von Intel und dem Auftragsfertigungsprozess von TSMC, um die neuesten Lion Cove P-Kerne zu Lunar Lake zu bringen und Intels IPC-Architektur so zu verbessern, wie Sie es von einer neuen Generation erwarten würden. Gleichzeitig bietet Intel auch Skymont E-Kerne an, die die Low Power Island Cresmont E-Core-Kerne von Meteor Lake ersetzen. Es ist jedoch erwähnenswert, dass diese E-Kerne nicht wie die P-Kerne mit dem Ringbus verbunden sind, was sie zu einer Art Hybrid-LP-E-Kern macht, der die Effizienzgewinne des fortschrittlicheren TSMC N3E-Knotens mit einem zweistelligen Zugewinn kombiniert IPC im Vergleich zu früheren Crestmont-Kernen.

Das gesamte Rechenboard, einschließlich der P- und E-Kerne, ist auf dem N3E-Knoten von TSMC aufgebaut, während das SoC-Board auf dem N6-Knoten von TSMC aufgebaut ist.

Auf einer höheren Ebene setzt Intel hier erneut auf seine Foveros-Verpackungstechnologie. Sowohl die Rechenplatine als auch die SoC-Platine (jetzt der „Plattform-Controller“) sind oben auf der Kernplatine platziert und ermöglichen so eine schnelle und stromsparende Weiterleitung zwischen den Kacheln sowie mehr Konnektivität zum Rest des Chips und darüber hinaus.

Als weiteres Novum für ein Mainstream-Intel-Core-Produkt verfügt der Lunar-Lake-SoC auch über bis zu 32 GB LPDDR5X-Speicher auf demselben Chippaket. Dieser ist als Paar von 64-Bit-Speicherchips angeordnet und bietet eine Gesamtspeicherschnittstelle von 128 Bit. Wie bei anderen Anbietern, die On-Package-Speicher verwenden, bedeutet diese Änderung, dass Benutzer DRAM nicht nach Belieben aufrüsten können und die Speicherkonfigurationen für Lunar Lake letztendlich von den SKUs bestimmt werden, die Intel ausliefert.

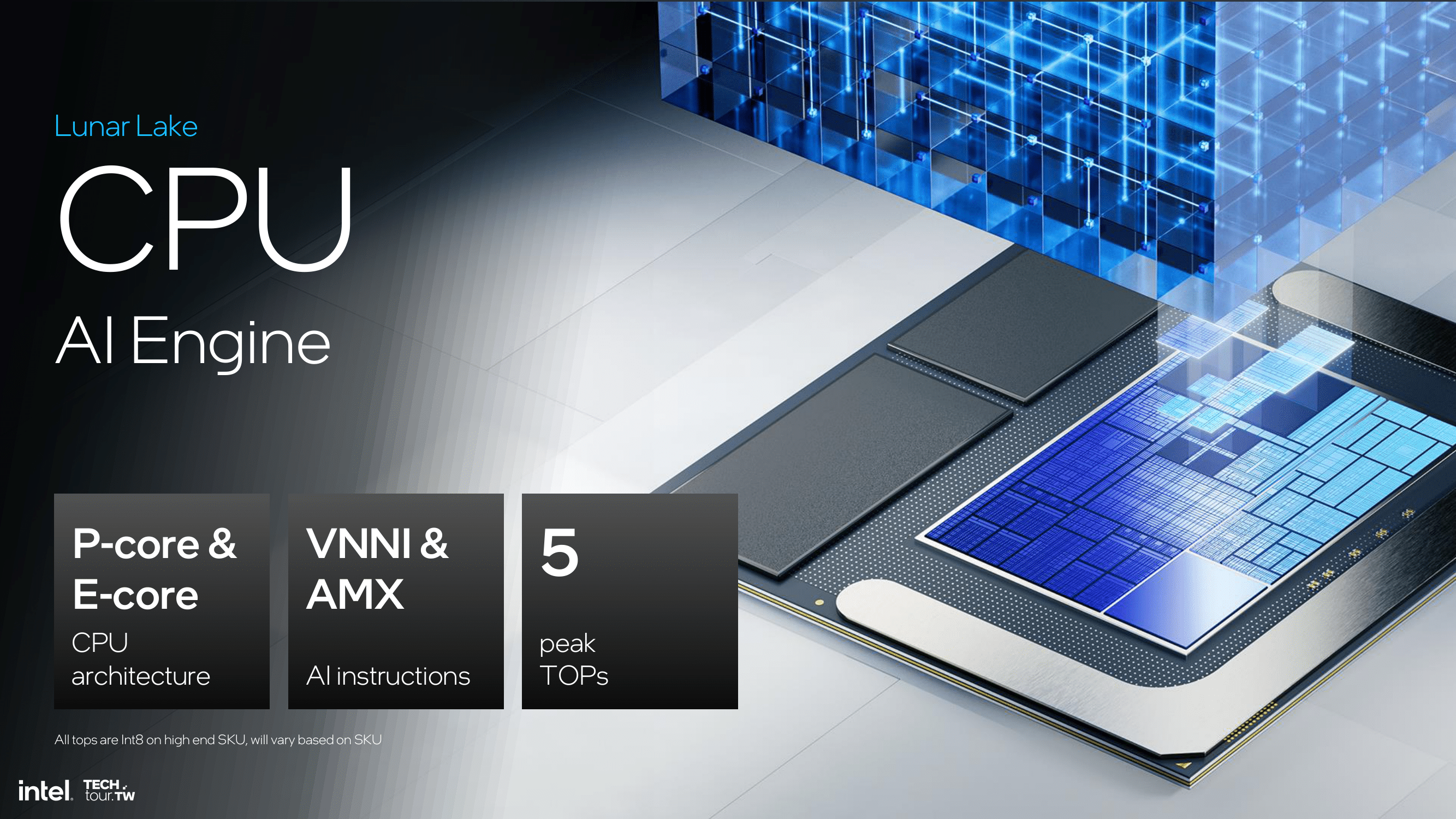

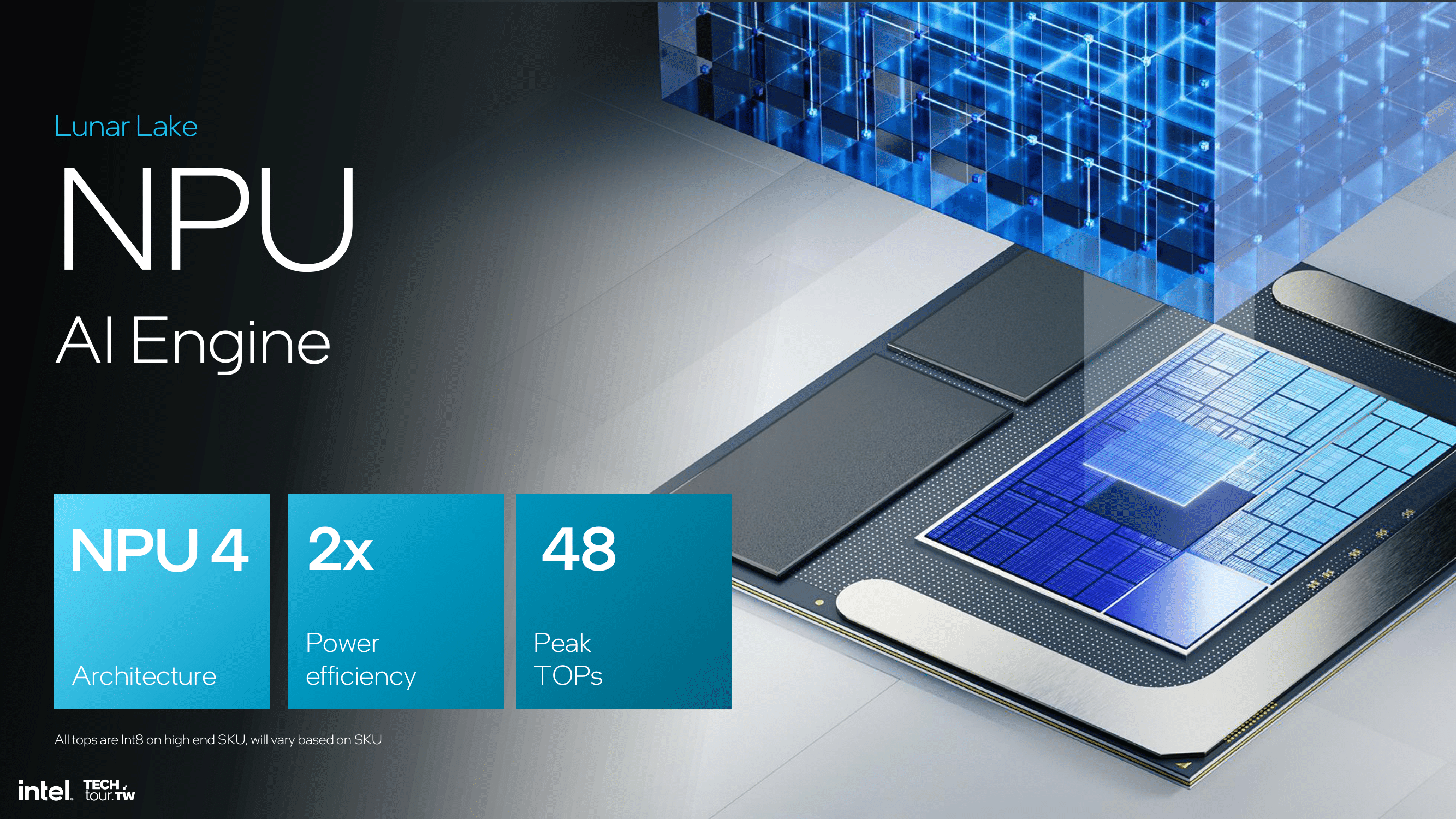

Mit Lunar Lake legt Intel auch einen starken Fokus auf KI, da die Architektur eine neue NPU namens NPU 4 integriert. Diese NPU ist für bis zu 48 TOPS der INT8-Leistung bewertet und somit PC-bereit für Microsoft Copilot+ AI. Dies ist das Ziel, das alle PC-SoC-Anbieter anstreben, darunter auch AMD und Qualcomm.

Auch die integrierte GPU von Intel wird hier einen Beitrag leisten. Auch wenn die Maschine nicht ganz so effizient ist wie eine dedizierte NPU, bringt die Arc Aus diesem Grund sehen Sie auch Intels Bewertung der Leistung dieser Chips im Hinblick auf die gesamten Plattformeindrücke – in diesem Fall 120 TOPS.

Die Zusammenarbeit von Intel mit Microsoft verbessert das Workload-Management durch den legendären Intel Thread Director, der für Anwendungen wie Copilot Assistant optimiert ist. Angesichts des Zeitpunkts der Einführung von Lunar Lake ebnet dies in gewisser Weise den Weg für eine Markteinführung im dritten Quartal 2024, das mit dem Weihnachtsmarkt 2024 zusammenfällt.

Intel Lunar Lake: Intel Series Manager-Update und Verbesserungen der Energieverwaltung

Zu sagen, dass Energieeffizienz ein Hauptziel für Lunar Lake ist, wäre eine Untertreibung. Obwohl Intel eine hohe Position auf dem Laptop-CPU-Markt einnimmt (der Anteil von AMD beträgt dort immer noch nur einen kleinen Bruchteil), geriet das Unternehmen in den letzten Jahren unter Druck durch den zum Kunden gewordenen Apple-Kunden, der die M-Serie von Apple besitzt Silizium hat in den letzten Jahren Maßstäbe für Energieeffizienz gesetzt. Jetzt versucht Qualcomm mit dem kommenden Snapdragon, dasselbe für das Windows-Ökosystem zu tun

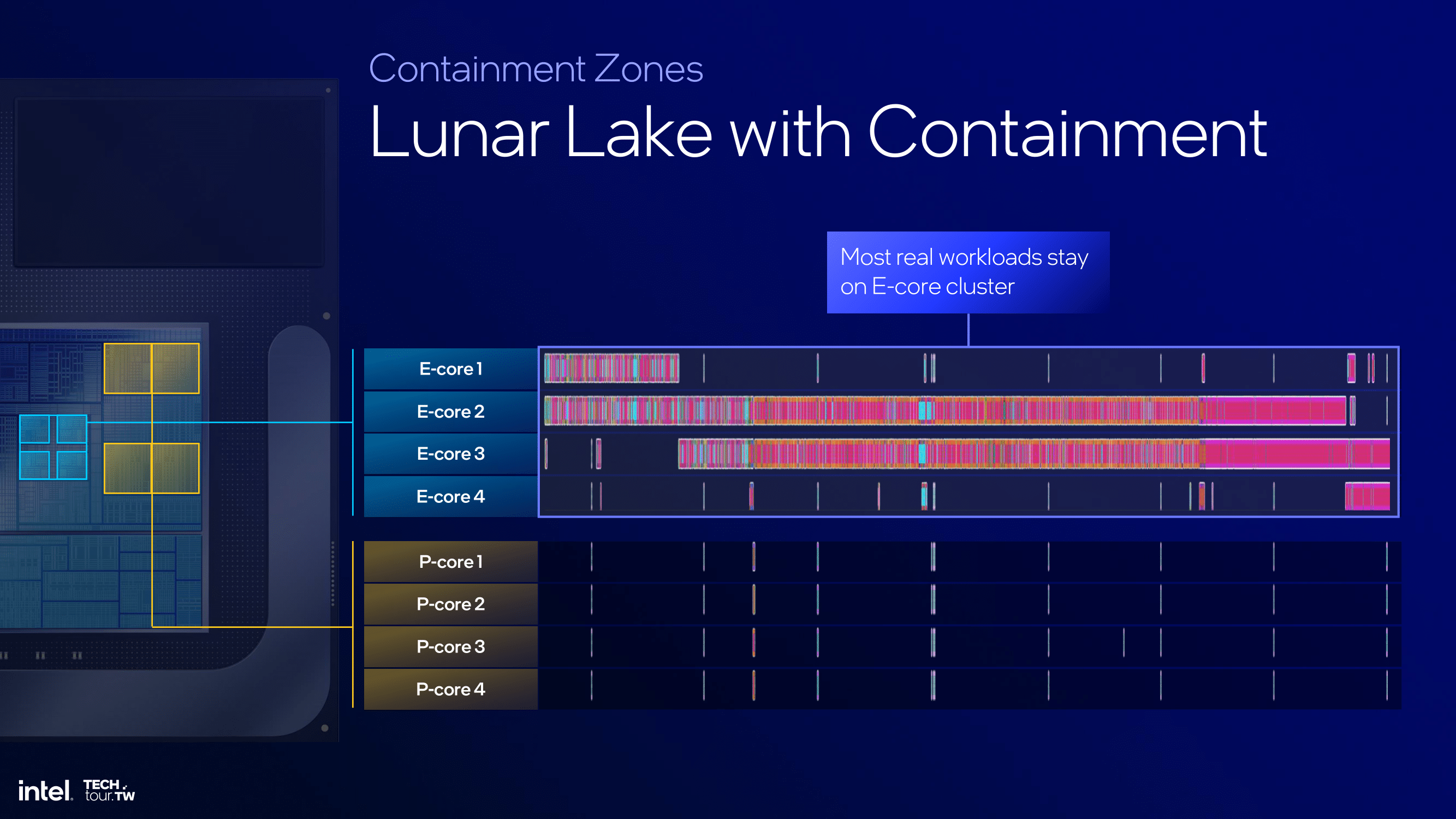

Intels Thread-Manager- und Energieverwaltungs-Updates für Lunar Lake zeigen verschiedene und signifikante Verbesserungen gegenüber Meteor Lake. Der Thread-Manager verwendet eine heterogene Planungsrichtlinie, bei der Aufgaben zunächst einem E-Core zugewiesen und bei Bedarf auf einen anderen E-Core oder P-Core ausgeweitet werden. OS-Containment-Zonen sind darauf ausgelegt, Aufgaben auf bestimmte Kerne zu beschränken, was die Energieeffizienz direkt verbessert und die Leistung bereitstellt, die der richtige Kernel für die jeweiligen Arbeitslasten benötigt. Die Integration mit Energieverwaltungssystemen und dem Quartett der Power Management Controller (PMC) des Chips in Abstimmung mit Windows 11 ermöglicht kontextbezogene Anpassungen und sorgt so für optimale Leistung bei minimalem Stromverbrauch und -verschwendung.

Die Planungsstrategie von Lunar Lake verarbeitet energieempfindliche Anwendungen effizient. Ein Beispiel von Intel ist, dass Videokonferenzaufgaben innerhalb des Effizienzkerns gehalten werden, wobei elektronische Kerne zur Aufrechterhaltung der Leistung eingesetzt werden und gleichzeitig der Stromverbrauch um bis zu 35 % gesenkt wird, wie aus den von Intel bereitgestellten Daten hervorgeht. Diese Verbesserungen werden durch die Zusammenarbeit mit Betriebssystementwicklern wie Microsoft für eine nahtlose Integration erreicht, um das beste Gleichgewicht zwischen Stromverbrauch und Leistung zu erreichen.

Intel konzentriert sich auf das Energieverwaltungssystem für Lunar Lake und verwendet ein eigenes Energiemanagement auf dem SoC, das in Effizienz-, Balance- und Leistungsmodi arbeitet, die speziell darauf ausgelegt sind, sich zur Laufzeit an alle Arbeitslastanforderungen anzupassen. Dieser mehrschichtige Ansatz ermöglicht einen effizienten Betrieb des Lunar Lake SoC. Auch hier können PMCs wie beim Intel Thread Director den Stromverbrauch mit den Leistungsanforderungen in Einklang bringen.

Intel plant außerdem, den Thread-Manager zu verbessern, indem die Granularität der Szenarien erhöht, KI-basierte Planungshinweise implementiert und Over-IP-Planung in Windows 11 ermöglicht wird. Diese Verbesserungen entsprechen im Wesentlichen einem Workload-Management, das darauf ausgelegt ist, die Gesamtenergieeffizienz zu steigern und Leistung über verschiedene Anwendungen hinweg bereitzustellen Sie werden benötigt, ohne das Energiebudget zu verschwenden, indem leichtere Aufgaben leistungsstärkeren P-Kernen zugewiesen werden.

Auf den nächsten Seiten werden wir uns mit den neuen P- und E-Kernen und Intels Update auf die integrierte Arc Xe-Grafik (Xe2-LPG) befassen.

„Hipsterfreundlicher Entdecker. Preisgekrönter Kaffeefan. Analyst. Problemlöser. Störenfried.“

More Stories

So verwandeln Sie Ihr Zuhause in eine echte Smart Home-Umgebung

Dieses 100-W-GaN-Ladegerät ist dünn und faltbar

Kuo: Das RAM-Upgrade auf 12 GB im nächsten Jahr wird auf das iPhone 17 Pro Max beschränkt sein